In the era of AI, everyone wants to communicate more interactively with an immediate or real time response. This leads to increase in devices with visual, input interfaces. With leading technology, the higher resolution displays with touch, voice or gesture-based inputs are today’s needs.

Such devices with high-definition screens and different input interfaces needs extensive computing and high performing hardware platforms. This in turn adds to the cost, which impacts to the scope and market use of these products.

The Human Machine Interfaces (HMI) is one of such products with variety of scope in application areas like automation, medical, automobile, industrial, commercial, domestic for interactive operations. The global HMI market size is estimated to worth $5.2Bn in 2023 and is projected to reach 2028 at CAGR of 8.2%.

The main component of these hardware platforms is micro-controller (MCU) unit, which alone contributes to approx. 15% of the total product cost. The high performing MCUs are too expensive than their low performing counter parts. The ARM Cortex M7 MCUs @800MHz are approx. 50% more expensive than similar MCUs @600MHz. Overall, for achieving approx. 25-35% higher performance the direct product cost gets increased by >10%.

The continuous upgrading of high performing platforms, indirectly raises other concerns like

- redesigning of hardware,

- compatibility concerns,

- add-on features,

- product reliability,

- meet the compliance

All these add to the development time and money.

Currently everyone is focused to use the high speed, high performing hardware to deliver the enhanced features, interactive logic with real time responses, with increasing cost to value ratio.

To save this cost and time, it is ensured that the available hardware resources are used efficiently and utilize any scope of improvement. This is done by maximizing the utilization of hardware resources by exploiting the peripheral modules with strong support of efficient programming.

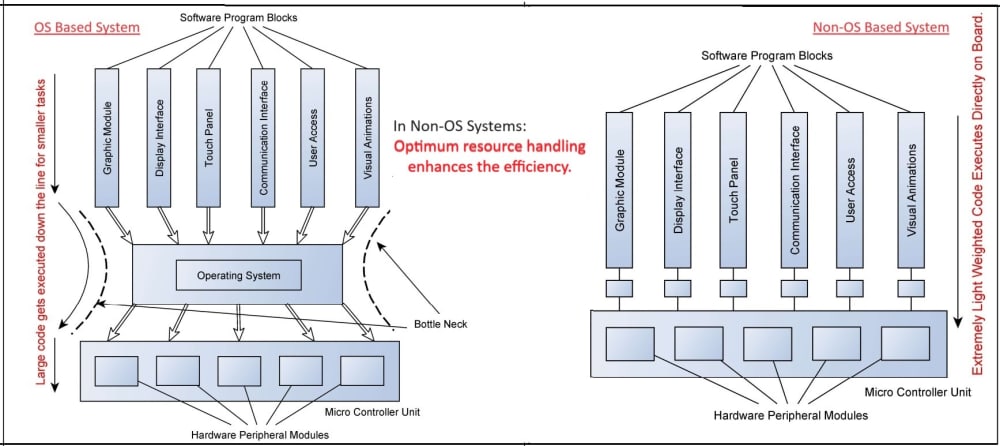

To enhance the resource utilization, efficient architecture is designed with extremely light weight codes, proper memory management, implementing modular blocks and effective priority assignment.

The Display Module is the key module heavily consuming the resources, speed and memory due to enhanced graphic effects. So, the graphic module is configured effectively, and its architecture is designed to use the hardware resources most efficiently. This enables to comparative high performance with a cost-effective solution.

This idea of delivering enhanced features with excellent visibility and real time interface by designing the efficient architecture instead of emphasizing on enhanced hardware is the innovative thought we proceed on.

The HMI with increased efficiency and performance fulfills the application needs like improved safety, enhanced productivity with better excellent visual, graphical representation of critical data, timely preventive maintenance.

Aiming maximum hardware utilization with cost optimized design General Industrial Controls Pvt. Ltd. has developed an HMI with high-performance real-time responses and enhanced display interface. We already manufactured and shipped more than 5000 HMI units with this upgrade. All these product improvements also yield in ease of production procedures, so reducing the manufacturing cost.

Like this entry?

-

About the Entrant

- Name:Manoj Rewatkar

- Type of entry:individual

- Patent status:none