BACKGROUND

- Rise of quantum computing threatens existing encryption schemes.

- NIST has standardized Post‐Quantum Cryptography (PQC) algorithms.

- A Quantum‐resistant Key Encapsulation Mechanism (KEM) based on the CRYSTALS‐Kyber algorithm was standardized as new Federal Information Processing Standards (FIPS).

- Kyber is based on the Module Learning with Errors (MLWE) problem which is based on lattice‐based cryptography.

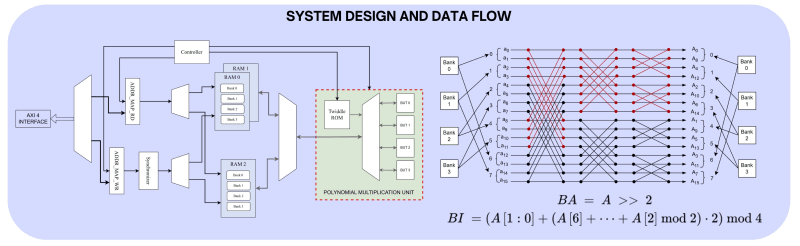

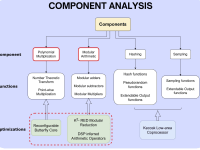

- MLWE requires computationally expensive modular polynomial multiplications.

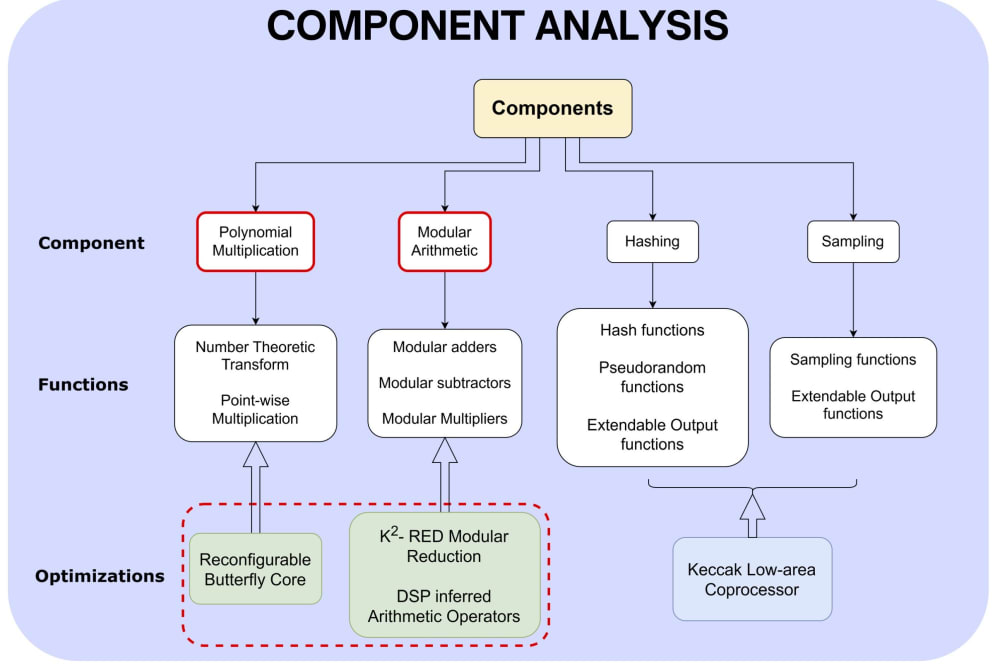

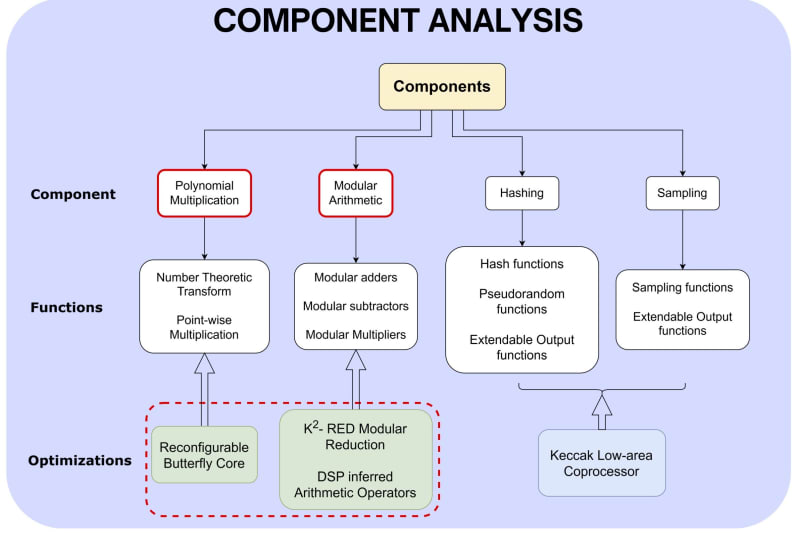

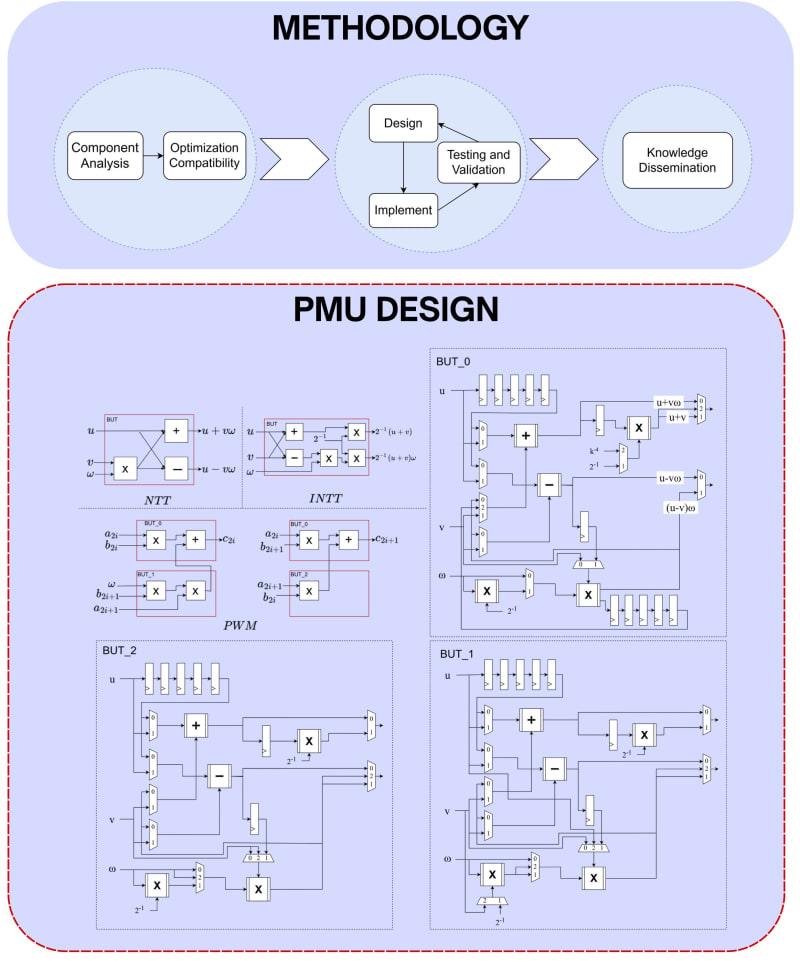

- Calculations can be optimized with efficient techniques like Number Theoretic Transform (NTT) and Pointwise Multiplication (PWM).

- Hardware accelerators are essential to perform these calculations efficiently

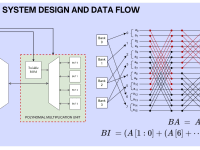

- Reconfigurable butterfly units incorporating modular arithmetic operators are the core accelerator components.

PROBLEMS

- FindF the performance critical components of the CRYSTALS‐Kyber PQC algorithm

- Find a comprehensive optimization strategy for a hardware accelerator

- Design a FPGA implementation of the optimized hardware accelerator

The advent of quantum computing presents a significant threat to classical encryption algorithms, necessitating the transition toward quantum-resistant cryptographic solutions. In response, the National Institute of Standards and Technology (NIST) has standardized several Post-Quantum Cryptography (PQC) algorithms. Among them, the CRYSTALS-Kyber Key Encapsulation Mechanism (KEM) stands out as a robust, quantum-secure solution. It is based on the Module Learning With Errors (MLWE) problem, a lattice-based cryptographic scheme that inherently demands intensive modular polynomial arithmetic.

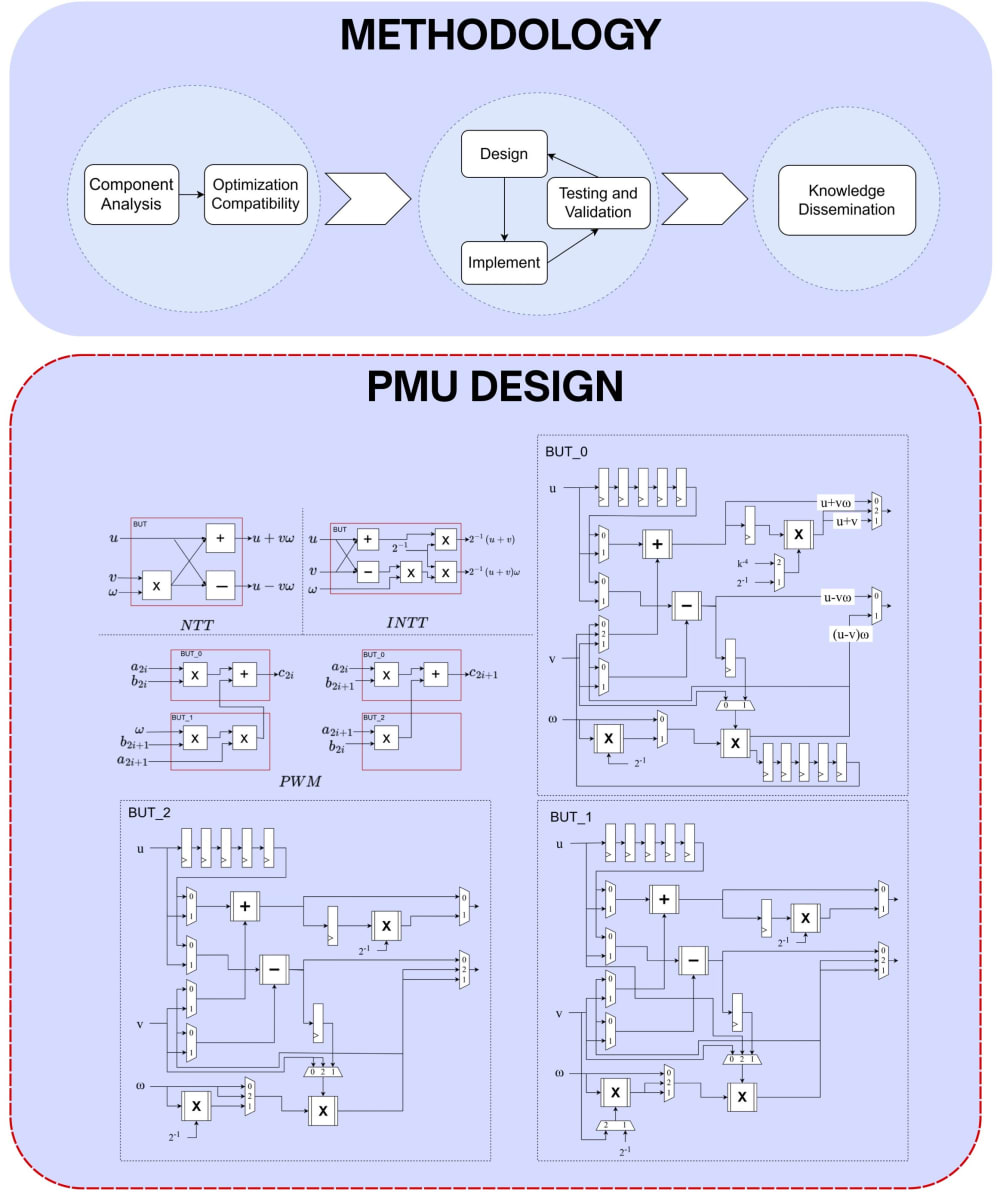

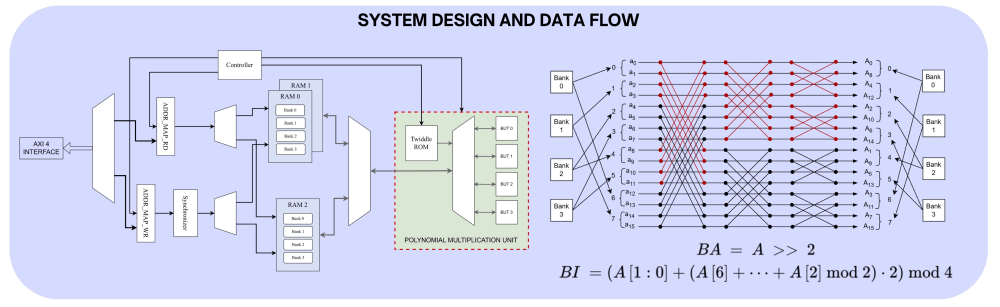

A reconfigurable hardware accelerator is designed using FPGA technology, targeting the Artix-7 XC7A100T development board. The architecture centers around a modular and reconfigurable butterfly processing unit, which incorporates efficient modular arithmetic operations. The design strategically utilizes the FPGA’s DSP slices to reduce both area and power consumption, making it ideal for low-resource, real-time applications.

The proposed system demonstrates an effective balance between performance and resource efficiency. Experimental results confirm the accelerator's ability to significantly enhance the speed of polynomial multiplications, while maintaining a compact hardware footprint. This makes the solution suitable for embedded cryptographic applications requiring high throughput with limited hardware resources.

This work contributes to the field by presenting a scalable and efficient hardware implementation of the CRYSTALS-Kyber algorithm, aligned with current post-quantum cryptographic standards.

Like this entry?

-

About the Entrant

- Name:Chathura Gunasekara

- Type of entry:individual

- Software used for this entry:Vivado 2024.2

- Patent status:none